# Port Bypass Circuits for Fibre Channel Arbitrated Loop Standard and its Extensions

# Technical Data

#### **Features**

- Supports 802.3z 1.25 Gbps Gigabit Ethernet (GE) Rates

- Single PBC, CDR, Dual Signal Detect (SD) in a Single Package

- Bidirectional, Symmetric Bypass Capability

- CDR in Bypass Path and Loop Path

- CDR Location Determined by Wiring Configuration of Pins on PCB (Patent Pending)

- Envelope Detect on Cable Input (SD) for Both Directions

- Equalizers On All Inputs

- High Speed PECL I/Os Referenced to  $V_{CC}$

- Buffered Line Logic (BLL)

Outputs without External

Bias Resistors

- 0.4 W Typical Power at  $V_{\rm CC}$  = 3.3 V

- 5 V Tolerant LVTTL I/O

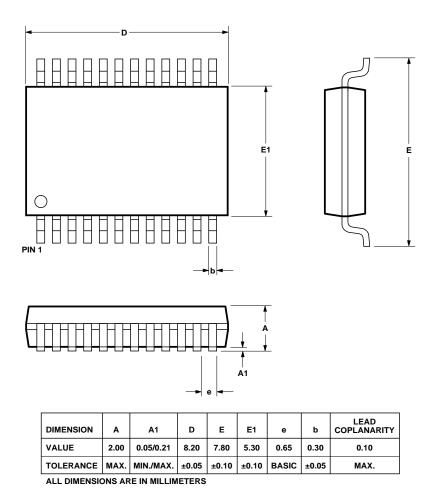

- 24 Pin SSOP Package

#### Applications

- RAID, JBOD Cabinets

- 1=>1 Gigabit Serial Buffer Pair (with and w/o CDR)

- Multi-Initiator Loops

#### **Description**

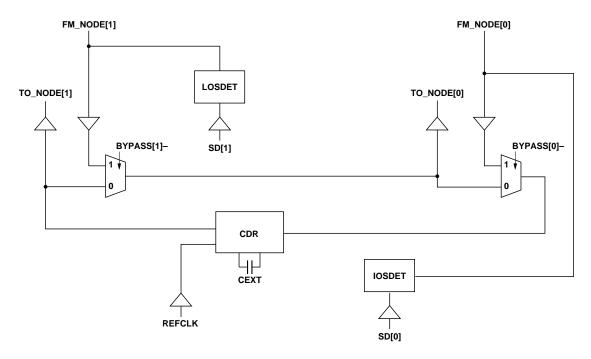

The HDMP-0421 is a Single Port Bypass Circuit (PBC) with Clock and Data Recovery (CDR), and dual Signal Detect (SD) capability. This configuration will control jitter accumulation while repeating incoming signals. Port Bypass Circuits are used to provide loops that are continuously on in hard disk arrays constructed in Fibre Channel Arbitrated Loop (FC-AL) configurations. Hard disks may be pulled out or swapped while other disks in the array are available to the system. This device may also be used in multi-initiator loop configurations.

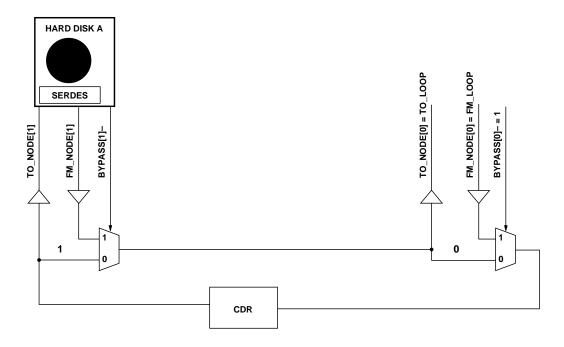

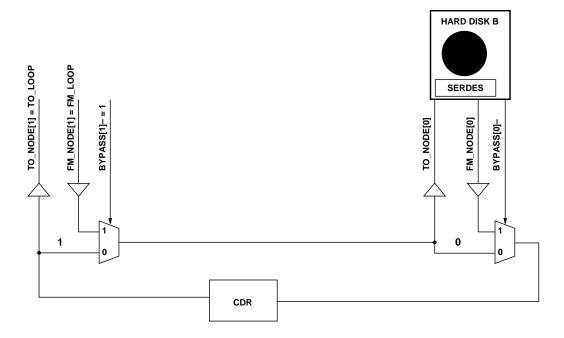

A Port Bypass Circuit is a 2:1 Multiplexer array with two modes of operation: DISK IN LOOP and DISK BYPASSED. In DISK IN LOOP mode, the loop goes into and out of the disk drive. Data go from the HDMP-0421's TO NODE[n]± differential output pins to the Disk Drive Transceiver IC (for example, an HDMP-1536A) Rx± differential input pins. Data from the Disk Drive Transceiver IC Tx± differential output pins go to the HDMP-0421's FM NODE[n]± differential input pins. Figures 4 and 5 show connection diagrams for disk drive array applications. In DISK BYPASSED mode, the disk drive is either absent or non-functional and the loop bypasses the hard disk. DISK IN LOOP mode is

# HDMP-0421 Single PBC & CDR

enabled with a HIGH on the BYPASS[n]– pin and DISK BYPASSED mode is enabled with a LOW on the same pin.

Multiple HDMP-0421s may be cascaded or connected to other members of the HDMP-04xx family through the FM\_LOOP and TO\_LOOP pins to create loops for arrays of disk drives. See Table 2 to identify which of the two cells (0:1) will provide FM\_LOOP, TO\_LOOP pins (cell connected to cable). ALL TO\_NODE outputs of the HDMP-0421 are of equal strength. Combinations of HDMP-04xx may be utilized to accommodate any number of hard disks.

The HDMP-0421 may also be used as a pair of 1=>1 buffers, one with a CDR and another without. For example, HDMP-0421 may be placed in front of a CMOS ASIC to clean the jitter of the outgoing signal (CDR path) and to better read the incoming signal (CDR-less path).

The design of the HDMP-0421 allows for placement of the CDR at one of two locations with respect to a hard disk slot. For example, if the BYPASS[0]– pin is HIGH and hard disk slot A is connected to PBC cell 1, the CDR function will be performed before entering the hard disk at slot A

(Figure 4). To achieve a CDR function after slot A, the BYPASS[1]– pin must be HIGH and hard disk slot A must be connected to PBC cell 0 (Figure 5). Table 2 shows both possible connections. In both cases, a Signal Detect (SD) pin

shows the status of the signal at the incoming cable. The recommended method of setting the BYPASS[i]– pins HIGH is to drive them with a high-impedence signal. Internal pullup resistors will force the BYPASS[I]– pins to  $V_{\rm CC}$ .

Figure 1. Block Diagram of HDMP-0421.

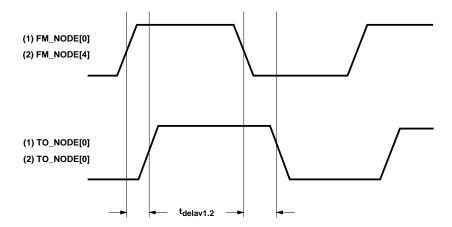

Figure 2. Timing Waveforms.

Table 1a. Truth Table for CDR at Entry Configurations

$FM_LOOP = FM_NODE[0], TO_LOOP = TO_NODE[0], BYPASS[0] = 1$

| TO_LOOP    | TO_NODE[1] | BYPASS[1]- |

|------------|------------|------------|

| FM_LOOP    | FM_LOOP    | 0          |

| FM_NODE[1] | FM_LOOP    | 1          |

### Table 1b. Truth Table for CDR at Exit Configurations

$FM_LOOP = FM_NODE[1], TO_LOOP = TO_NODE[1], BYPASS[1]-= 1$

| TO_LOOP    | TO_NODE[0] | BYPASS[0]- |

|------------|------------|------------|

| FM_LOOP    | FM_LOOP    | 0          |

| FM_NODE[0] | FM_LOOP    | 1          |

# Table 2. Pin Connection Diagram to Achieve Desired CDR Location (see Figures 4 and 5)

X Denotes CDR Position with respect to Hard Disks

| Hard Disk               | A  | A  |

|-------------------------|----|----|

| Connection to PBC Cells | 1  | 0  |

| CDR Position (x)        | xA | Ax |

| Cell Connected to Cable | 0  | 1  |

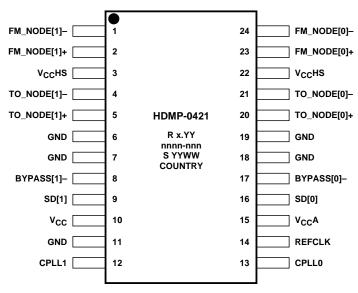

nnnn.nnn = WAFER LOT - BUILD NUMBER (1-3 DIGITS)

Rx.yy = DIE REVISION

S = SUPPLIER CODE

YYWW = DATE CODE (YY = YFAR WW = WORK WEFK)

YYWW = DATE CODE (YY = YEAR, WW = WORK WEEK)

COUNTRY = COUNTRY OF MANUFACTURE

Figure 3: HDMP-0421 Package Layout and Marking, Top View.

Table 3. Pinout

| Pin Name          | Pin             | Pin Type | Pin Description                                                                         |

|-------------------|-----------------|----------|-----------------------------------------------------------------------------------------|

| TO_NODE[0]+       | 20              | O-PECL   | In CDR at entry configuration, this pin is the Serial Output                            |

|                   |                 |          | (TO_LOOP+). In other configurations, this pin is wired to the hard disk.                |

| TO_NODE[0]-       | 21              | O-PECL   | In CDR at entry configuration, this pin is the Serial Output                            |

|                   |                 |          | (TO_LOOP–). In other configurations, this pin is wired to the hard disk.                |

| FM_NODE[1]+       | 02              | I-PECL   | Input from Transceiver IC to Cell 1.                                                    |

| FM_NODE[1]-       | 01              | I-PECL   | Input from Transceiver IC to Cell 1.                                                    |

| TO_NODE[1]+       | 05              | O-PECL   | Output to Transceiver IC from Cell 1.                                                   |

| TO_NODE[1]-       | 04              | O-PECL   | Output to Transceiver IC from Cell 1.                                                   |

| FM_NODE[0]+       | 23              | I-PECL   | In CDR at entry configuration, this pin is the Serial Input                             |

|                   |                 |          | (FM_LOOP+). In other configurations, this pin is wired to the hard disk.                |

| FM_NODE[0]-       | 24              | I-PECL   | In CDR at entry configuration, this pin is the Serial Input                             |

|                   |                 |          | (FM_LOOP–). In other configurations, this pin is wired to the hard disk.                |

| BYPASS[1]-        | 08              | I-LVTTL  | Bypass pin for cell 1. In CDR at exit configuration, float to HIGH else                 |

|                   |                 |          | ground connect through a 1 K $\Omega$ resistor.                                         |

| BYPASS[0]-        | 17              | I-LVTTL  | Bypass pin for cell 0. In CDR at exit configuration, float to HIGH else                 |

|                   |                 |          | ground connect through a 1 K $\Omega$ resistor.                                         |

| REFCLK            | 14              | I-LVTTL  | Reference Clock Input for Clock and Data Recovery (CDR) circuit.                        |

| CPLL1             | 12              | С        | PLL cap pin. Connected to pin 13 with a 0.1 microFarad capacitor.                       |

| CPLL0             | 13              | С        | PLL cap pin. Connected to pin 12 with a 0.1 microFarad capacitor.                       |

| SD[1]             | 09              | O-LVTTL  | Signal Detect via envelope detect method. In CDR at entry and at exit                   |

| SD[0]             | 16              |          | cases, detects signal on incoming cable respectively. Active High when                  |

|                   |                 |          | signal is detected.                                                                     |

|                   |                 |          | If $(FM_NODE[0] + -FM_NODE[0] -) > = 400 \text{ mV peak-to-peak}$ , $SD = 1$            |

|                   |                 |          | If $400 \text{ mV} >= (\text{FM\_NODE}[0] + -\text{FM\_NODE}[0] -) >= 100 \text{ mV}$ , |

|                   |                 |          | SD = unpredictable<br>If $100 \text{ mV} >= (FM_NODE[0] + -FM_NODE[0] -)$ , $SD = 0$    |

| GND               |                 | S        | 6, 7, 11, 18, 19 Ground pins.                                                           |

|                   | 15              | S        | Analog Power Supply pin.                                                                |

| V <sub>CC</sub> A |                 |          | 9 11 0 1                                                                                |

| $V_{CC}HS$        | $\frac{03}{22}$ | S<br>S   | Cell 1 High Speed Output Pins Power Supply. Cell 0 High Speed Output Pins Power Supply. |

| 17                |                 | S        |                                                                                         |

| $V_{\rm CC}$      | 10              | 5        | Logic Power Supply pins.                                                                |

Figure 4: Connection Diagram. Case of CDR Before Entering the Hard Disk.

$\label{eq:connection Diagram. Case of CDR After Exiting the Hard Disk. }$

### **Absolute Maximum Ratings**

$T_A = 25$ °C, except as specified. Operation in excess of any one of these conditions may result in permanent damage to this device.

| Symbol                | Parameter                   |                      | Min. | Max.         |

|-----------------------|-----------------------------|----------------------|------|--------------|

| $V_{\rm CC}$          | Supply Voltage              | V                    | -0.7 | 4.0          |

| V <sub>IN,LVTTL</sub> | LVTTL Input Voltage         | V                    | -0.7 | 4.0          |

| V <sub>IN,HS_IN</sub> | HS_IN Input Voltage         | V                    | 2.0  | $V_{\rm CC}$ |

| $I_{O,LVTTL}$         | LVTTL Output Source Current | mA                   |      | ± 13         |

| $T_{ m stg}$          | Storage Temperature         | $^{\circ}\mathrm{C}$ | -65  | +150         |

| Tj                    | Junction Temperature        | $^{\circ}\mathrm{C}$ | 0    | +125         |

# Guaranteed Operating Rates $T_A=0\,^{\circ}\!\mathrm{C}$ to +70°C, $V_{CC}=3.15~V$ to 3.45~V

| Serial Clock Rate<br>FC (MBd) |      | Serial Clock Rate<br>GE (MBd) |      |  |

|-------------------------------|------|-------------------------------|------|--|

| Min.                          | Max. | Min.                          | Max. |  |

| 1040 1080                     |      | 1240                          | 1260 |  |

### **Clock and Data Recovery Circuit Reference Clock Requirements**

$T_A = 0$ °C to +70°C,  $V_{CC} = 3.15$  V to 3.45 V

| Symbol | Parameter             | Unit | Min. | Тур.   | Max. | Min. | Тур.   | Max. |

|--------|-----------------------|------|------|--------|------|------|--------|------|

| f      | Nominal Frequency     | MHz  |      | 106.25 |      |      | 125.00 |      |

| Ftol   | Frequency Tolerance   | ppm  | -100 |        | +100 | -100 |        | +100 |

| Symm   | Symmetry (Duty Cycle) | %    | 40   |        | 60   | 40   |        | 60   |

### **DC Electrical Specifications**

$T_A = 0$ °C to +70°C,  $V_{CC} = 3.15$  V to 3.45 V

| Symbol                | Parameter                                                                            |    | Min. | Typ.  | Max. |

|-----------------------|--------------------------------------------------------------------------------------|----|------|-------|------|

| V <sub>IH,LVTTL</sub> | LVTTL Input High Voltage Range                                                       | V  | 2    |       | 4.0  |

| V <sub>IL,LVTTL</sub> | LVTTL Input Low Voltage Range                                                        | V  | 0    |       | 0.8  |

| V <sub>OH,LVTTL</sub> | LVTTL Output High Voltage Level, $I_{OH} = -400 \mu A$                               | V  | 2.2  |       | 3.45 |

| V <sub>OL,LVTTL</sub> | LVTTL Output Low Voltage Level, $I_{OL} = 1 \text{ mA}$                              | V  | 0    |       | 0.6  |

| I <sub>IH,LVTTL</sub> | Input High Current (Magnitude), $V_{IN} = 2.4 \text{ V}$ , $V_{CC} = 3.45 \text{ V}$ | μΑ |      | 0.003 | 40   |

| I <sub>IL,LVTTL</sub> | Input Low Current (Magnitude), V <sub>IN</sub> = 0.4 V, V <sub>CC</sub> = 3.45 V     | μΑ |      | 300   | 600  |

| $I_{CC}$              | Total Supply Current, T <sub>A</sub> = 25°C                                          | mA |      | 110   |      |

| Symbol                  | Parameter                                                             | Units | Min. | Тур. | Max. |

|-------------------------|-----------------------------------------------------------------------|-------|------|------|------|

| $t_{ m delay1}$         | Total Loop Latency from FM_NODE[0] to TO_NODE[0]                      | ns    |      | 4.0  |      |

| $t_{ m delay2}$         | Per Cell Latency from FM_NODE[4] to TO_NODE[0]                        | ns    |      | 2.0  |      |

| $t_{r,LVTTLin}$         | Input LVTTL Rise Time Requirement, 0.8 V to 2.0 V                     | ns    |      | 2.0  |      |

| t <sub>f,LVTTLin</sub>  | Input LVTTL Fall Time Requirement, 2.0 V to 0.8 V                     | ns    |      | 2.0  |      |

| $t_{r,LVTTLout}$        | Output LVTTL Rise Time Range, 0.8 V to 2.0 V, 10 pF Load              | ns    |      | 1.5  | 2.4  |

| t <sub>f,LVTTLout</sub> | Output LVTTL Fall Time Range, 2.0 V to 0.8 V, 10 pF Load              | ns    |      | 2.0  | 3.5  |

| trs, HS_OUT             | HS_OUT Single-Ended Rise Time                                         | ps    |      | 200  | 350  |

| t <sub>fs,HS_OUT</sub>  | HS_OUT Single-Ended Fall Time                                         | ps    |      | 200  | 350  |

| trd, HS_OUT             | HS_OUT Differential Rise Time                                         | ps    |      | 200  | 350  |

| tfd,HS_OUT              | HS_OUT Differential Fall Time                                         | ps    |      | 200  | 350  |

| V <sub>IP,HS_IN</sub>   | HS_IN Input Peak-To-Peak Required Differential Voltage Range          | mV    | 200  | 1200 | 2000 |

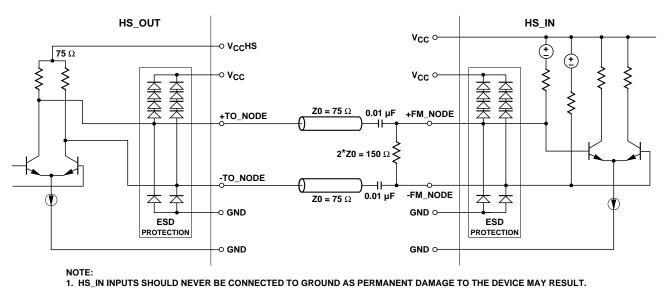

| V <sub>OP,HS_OUT</sub>  | HS_OUT Output Peak-To-Peak Differential Voltage (Z0=750 Ω, Figure 10) | mV    | 1100 | 1400 | 2000 |

# Power Dissipation and Thermal Resistance $T_A=0^{\circ}C$ to $+70^{\circ}C,~V_{CC}=3.15~V$ to 3.45~V

| Symbol           | Parameter                            | Unit | Typ. | Max. |

|------------------|--------------------------------------|------|------|------|

| $P_{\mathrm{D}}$ | Power Dissipation                    | mW   | 360  |      |

| $\Theta_{ m jc}$ | Thermal Resistance, Junction to Case | °C/W | 14   |      |

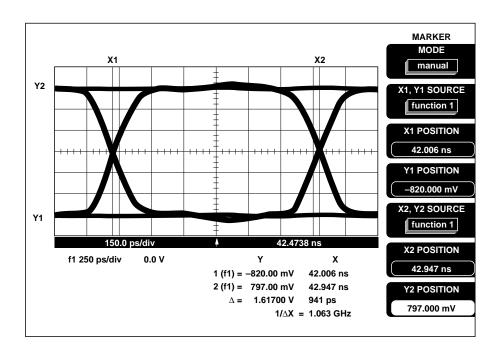

# **Output Jitter Characteristics**

$T_A = 0$ °C to +70°C,  $V_{CC} = 3.15$  V to 3.45 V

| Symbol | Parameter                                    | Unit | Тур. | Max. |

|--------|----------------------------------------------|------|------|------|

| RJ     | Random Jitter at TO_NODE pins (1 sigma rms)  | ps   | 6    |      |

| DJ     | Deterministic Jitter at TO_NODE pins (pk-pk) | ps   | 16   |      |

#### Note:

Please refer to Figures 7 and 8 for jitter measurement setup information.

**Locking Characteristics**  $T_A = 0$ °C to +70°C,  $V_{CC} = 3.15$  V to 3.45 V

| Parameter                  | Unit | Max. |

|----------------------------|------|------|

| Bit Sync Time (phase lock) | bits | 2500 |

| Frequency Lock at Powerup  | μs   | 500  |

Figure 6. Eye Diagram of a High Speed Differential Output.

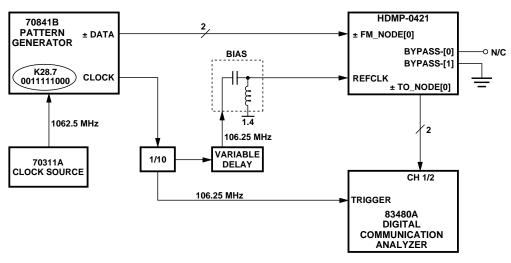

# RANDOM JITTER

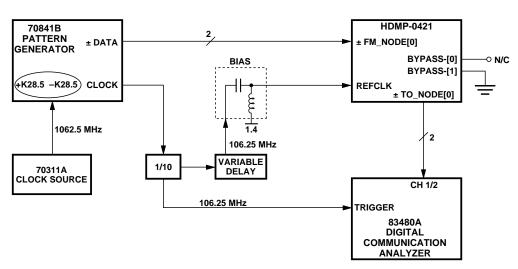

Figure 7. Setup for Measurement of Random Jitter.

#### **DETERMINISTIC JITTER**

Figure 8. Setup for Measurement of Deterministic Jitter.

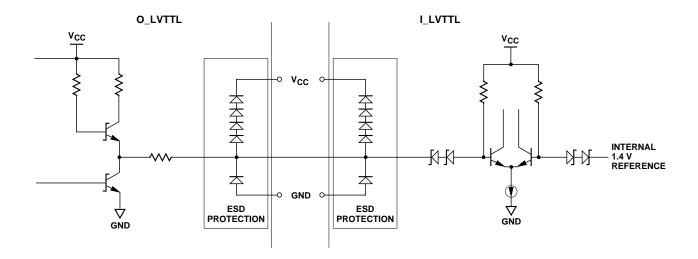

Figure 9. O-LVTTL and I-LVTTL Simplified Circuit Schematic.

Figure 10. O-PECL and I-PECL Simplified Circuit Schematic.

Figure 11. HDMP-04221 Package Drawings.